# THERMAL ISSUES IN ELECTRONICS APPLICATIONS

J. Richard Culham Department of Mechanical Engineering University of Waterloo

University of Water100

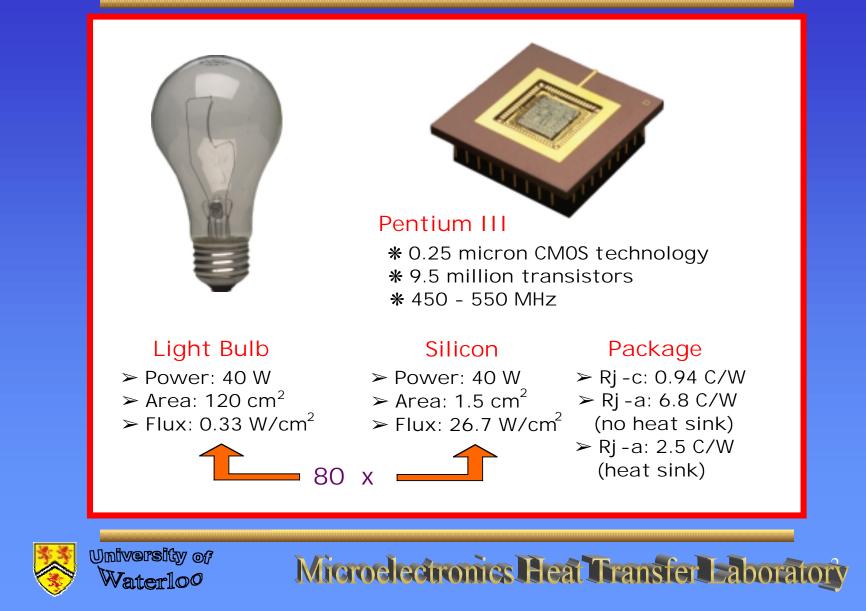

## 40 Watts! What's the big deal?

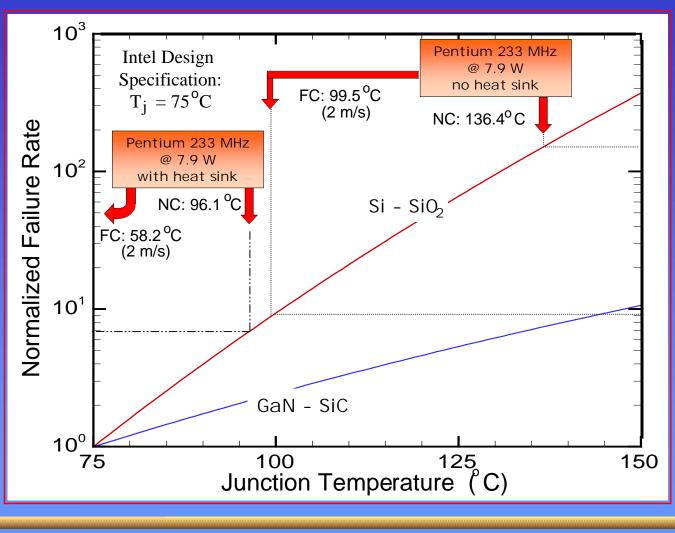

## **Component Failure Rate**

University of Water100

# Moore's Law (1965)

- each new chip contains roughly twice as much capacity as its predecessor

- a new generation of chips is released every18 24 months

#### From: www.intel.com

in 26 years, the population of transistors per chip has increased by 3,200 times

University of Waterloo

### IC Trends: Past, Present & Future

|                    | 1980  | 1999  | 2003 | 2006 | 2012  |

|--------------------|-------|-------|------|------|-------|

| Comp. Per Chip     | 0.2 M | 6.2 M | 18 M | 39 M | 100 M |

| Frequency (MHz)    | 5     | 1250  | 1500 | 3500 | 10000 |

| Chip Area (sq. cm) | 0.4   | 4.45  | 5.60 | 7.90 | 15.80 |

| Max. Power (W)     | 5     | 90    | 130  | 160  | 175   |

| Junction Temp. (C) | 125   | 125   | 125  | 125  | 125   |

From: David L. Blackburn, NIST

# What Does The Future Hold?

• More of the same?

- higher packaging densities

- higher heat fluxes

- Can we rely on a technology break through?

ie. Bipolar

→ CMOS →?

- Thermal design tools must become part of a fully integrated design tool set

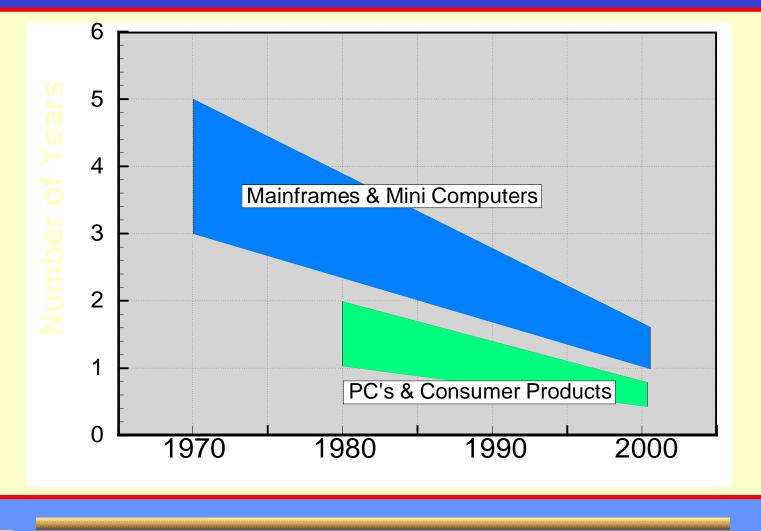

# **Design Challenges**

- Reduce design cycle times to a minimum

- numerical simulation and prototype testing are becoming less viable

- especially during preliminary design cycles

- optimization tools

- Concurrent design

- requires multidisciplinary skills

- simplicity is imperative

# Product Design Cycle

# Future Considerations

- Optimization tools

- faster models

- I/O portability for concurrent designs

- Improved access to design tools

- web tools

- extranets

- machine portability

- standardized test methods